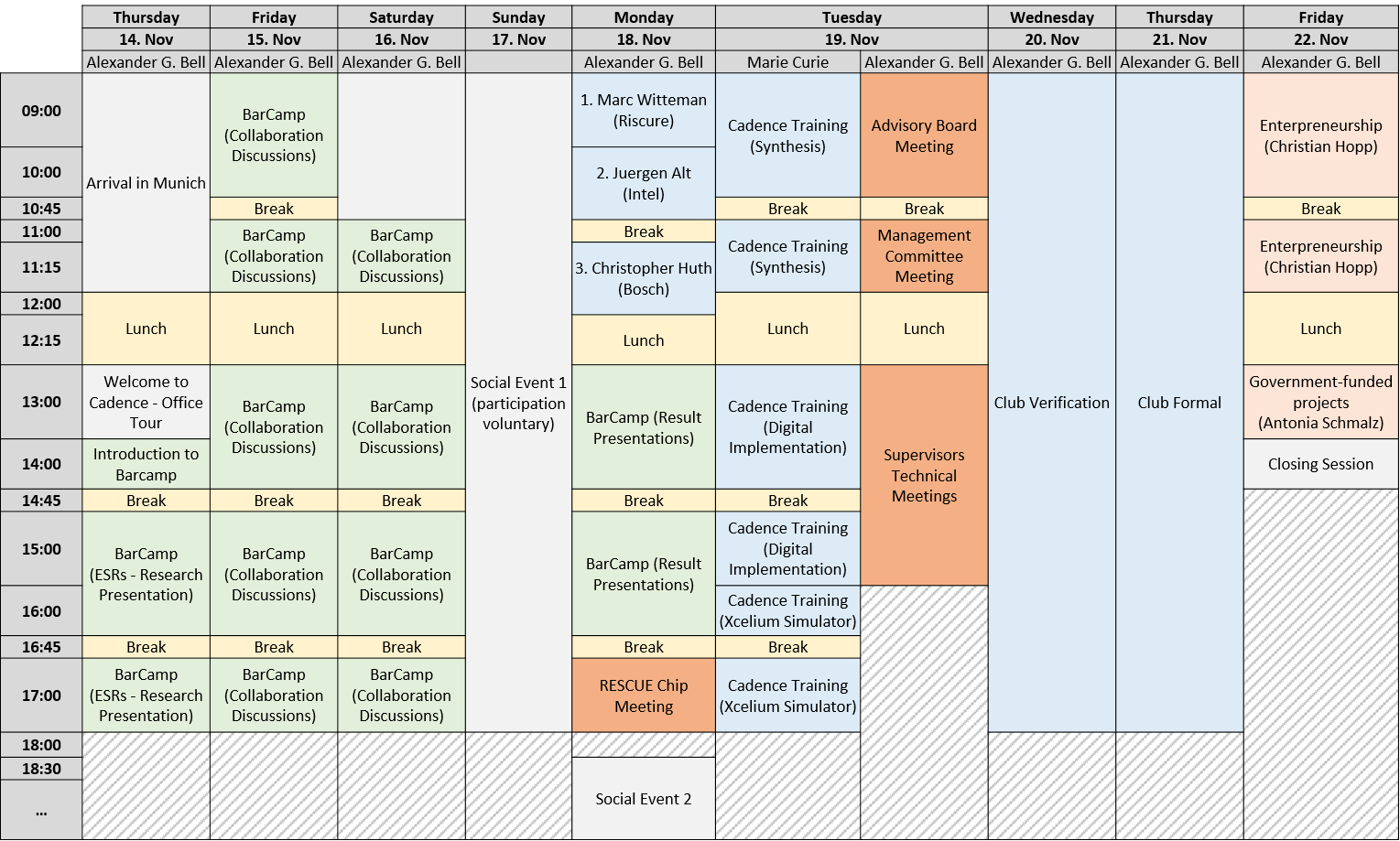

Cadence Design Systems organises the 3rd internal RESCUE ETN Winter Workshop November 14-22, 2019. The event will be held in Feldkirchen (vicinity of Munich), Germany. The event will start with a 3-day BarCamp ad-hoc gathering for the ESRs interact and discuss research topics in an open environment. The aim is to identify a set of collaboration clusters where the synergy of the competences is the most promising and to establish sub-projects to be led by ESRs themselves. The technical training on nanoelectronic systems design aspects will be provided by the key industrial players in the domain Intel, Riscure, Bosch, Cadence. Complementary skills training puts emphasis on development of the entrepreneurship skills enhancing knowledge in research funding options at European and regional levels.

The General Chair for the 3nd RESCUE Winter Workshop is Anton Klotz, Cadence.

Agenda

November 14-18 - BarCamp discussions and presentations by ESRs

November 18 - Technical training

“Why is it so hard to make secure chips?” - Marc Witteman, Riscure

Abstract: As our understanding of security threats and mitigations keeps growing one would expect chips to become more robust and have better resistance against attacks. Reality is different: the number of security issues is still going up, and vendors have huge challenges to keep products secure in the field. In this presentation we explore the various attack vectors and how they affect the chip design process. We conclude by sharing some concrete advice on how to reduce security risk.

“Specialization drives Semiconductors: View on Manufacturing Test” - Juergen Alt, Intel

Abstract: In Semiconductor business we are facing a continuous pressure for innovation. Key elements to drive innovation are partitioning and specialization on all levels. This talk gives some general thoughts on partitioning and specialization. An introduction into manufacturing test is used as an example for these general principles.

“Continuous Security Testing” - Christopher Huth, Bosch

Abstract: In times of large scale software projects and ongoing digitalization, automated security analysis methods are an important measure for enhancing software security and robustness. To put this into practice, we develop a prototypical platform to perform continuous security testing during development. This platform supports dynamic and static analysis methods and is flexible to be extended with various other analysis methods or targets. Fuzzing, a dynamic software testing technique coined by Miller et al., proofed tremendously beneficial for finding bugs. As a static analysis method we rely on Code Property Graphs, introduced by Yamaguchi et al., which combine the abstract syntax tree, control flow graph, and program dependence graph of a program into a single graph. Our work aims to reduce manual effort in software analysis. First, our platform automates security tests in a CI/CD style. Second, we automatically analyze existing module tests and generate fuzz test harnesses.

November 19 - Technical Training

“Digital Synthesis Training” - Cadence Design Systems

“Implementation Training” - Cadence Design Systems

Management Committee Meeting

Advisory Board Meeting

Technical Meetings

November 20 - Cadence ClubVerification

November 21 - Cadence ClubFormal

Program (including a talk by RESCUE ESR)

Xinhui Anna Lai, Maksim Jenihhin, Jaan Raik, Kolin Paul "On Verification For Timing Side Channel Using Cadence JasperGold SPV"

November 22 - Transferable skills training

“Lecture on entrepreneurship” - Christian Hopp, RWTH Aachen

Syllabus: What is Entrepreneurship? Different Approaches to Entrepreneurial Behavior. Problem Based Thinking. Business Model Design and Innovation. Speech, Rhetorics, and Business Idea Pitching.

“Government-funded projects” - Antonia Schmalz, VDI/VDE Innovation + Technik GmbH